第11回野口研究奨励賞

上野知洋 (うえの ともひろ)東北大学 大学院 情報科学研究科

[研究の概要]

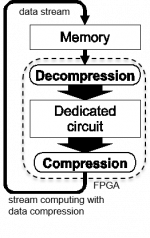

メモリ帯域の不足は,計算機性能を低下させる大きな要因の一つである.計算機システムにおけるメモリ帯域の向上は困難であるため,データ圧縮を用いて物理的な改良なしに実効帯域を向上させる手法が提案されている.これは,高スループットなハードウェア処理により,メモリとプロセッサ間の通信データを圧縮し,実効メモリ帯域を向上させる試みである.特に大規模なデータを用いる数値シミュレーションなどにおいて,メモリ帯域不足を解消し,計算性能の向上手段として期待されている.

今回受賞対象となった論文では,FPGAに実装した専用計算コアを用いたストリーム計算において,数値データストリームを効果的に圧縮するハードウェアのパラメータ化と実機における評価とを行っている.先行研究において提案された数値データ圧縮ハードウェアを,様々なビット幅のデータに対応させて評価を行い,実際の数値計算への適用について考察を行っている.実装したハードウェアは,データのビット幅の増加に伴い回路面積の増加と動作周波数の低下が見られたが,単精度,倍精度データの圧縮についてはいずれも高い性能を示している.また,圧縮性能の評価では,単精度,倍精度ともに汎用の圧縮スキームであるbzip2を超える性能を示している.これらの結果により,提案したハードウェアが小面積かつ高スループットであり,圧縮性能においても数値データの圧縮に適していることが示されている.

今回受賞対象となった論文では,FPGAに実装した専用計算コアを用いたストリーム計算において,数値データストリームを効果的に圧縮するハードウェアのパラメータ化と実機における評価とを行っている.先行研究において提案された数値データ圧縮ハードウェアを,様々なビット幅のデータに対応させて評価を行い,実際の数値計算への適用について考察を行っている.実装したハードウェアは,データのビット幅の増加に伴い回路面積の増加と動作周波数の低下が見られたが,単精度,倍精度データの圧縮についてはいずれも高い性能を示している.また,圧縮性能の評価では,単精度,倍精度ともに汎用の圧縮スキームであるbzip2を超える性能を示している.これらの結果により,提案したハードウェアが小面積かつ高スループットであり,圧縮性能においても数値データの圧縮に適していることが示されている.

[受賞の感想]

野口研究奨励賞という非常に名誉ある賞を受賞することが出来,大変光栄に存じます.同時に,情報処理学会東北支部の皆様に深く感謝申し上げます.本研究は,佐野健太郎先生,山本悟先生,古澤卓先生による多大なるご指導と,多くの方々のご支援により遂行できたものと思っております.皆様には厚く御礼申し上げます.今後も情報処理分野の発展のため,力を尽くしてまいります.